IBM reinvents AI computing by using analogue computing for artificial intelligence

IBM researchers have published a paper on a breakthrough in using analogue computing for artificial intelligence (AI).

When building an AI system, the data model needs to be trained. It is the process of assigning different weights to different subsets of the training data, such as image data describing different features of cats.

When AI systems are trained on traditional (digital) computers, the AI models are scattered and stored in memory. Computational tasks require constant transfer of data between memory and processing units.IBM says this process slows down computation and limits the upper limit of energy efficiency that can be achieved.

Using analogue computing for AI may provide a more efficient way to achieve the same results as AI running on digital computers.IBM defines analogue memory computing, or analogue AI, as a technology that draws on key features of the way neural networks operate in biological brains. In the brains of humans and many other animals, the strength of synapses, called weights, determines the communication between neurons, the researchers said.

In a simulated AI system, these synaptic weights are stored in situ in the conductance values of nanoscale resistive memory devices like phase change memory (PCM), IBM said. They are then used in deep neural networks to perform cumulative multiplication operations.

IBM says the technology reduces the need to constantly send data between memory and processors.

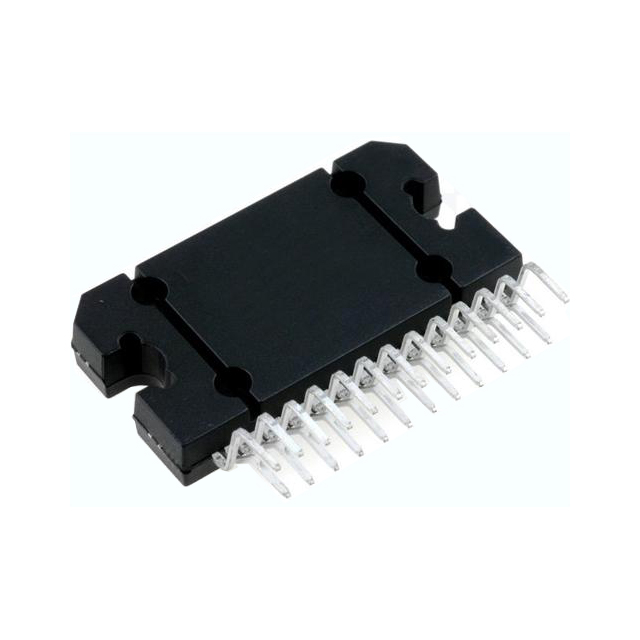

In a paper published in Nature Electronics, IBM Research describes a mixed-signal analogue AI chip that can run a variety of deep neural network (DNN) inference tasks. According to IBM, this is the first analogue chip that is on par with digital chips in performing computer vision AI tasks in tests, and is more energy efficient than the latter.

The chip was fabricated at IBM's Albany Nanotechnology Centre. It consists of 64 analogue memory computing cores (or chips), each containing a 256 x 256 cross array of synaptic units.IBM says time-based analogue-to-digital converters are integrated into each chip to convert between analogue and digital data. Each chip also incorporates lightweight digital processing units that IBM says perform non-linear neuron activation functions and scaling operations.

Each chip can perform a layer of DNN model-related computations, IBM said. The authors of the paper said, "Using the chip, we performed the most comprehensive study of computational accuracy for simulated in-memory computation and achieved 92.81 per cent accuracy on the CIFAR-10 image dataset."

Source: TopNet Software & Services Channel

Please contact us if the source is mislabeled or violates your legal rights.

We will promptly correct and delete, thank you.

- How TI’s investments in back-end manufac...

- Analog Devices Invests More Than $1 Bill...

- Analog Devices Releases 2022 Environment...

- IBM reinvents AI computing by using anal...

- Expert blog post Reducing Pin Usage in 8...

- Infineon's New Generation of Industrial ...

- How do I measure the light intensity of ...

- Microchip's New Cost-Effective Standalon...

- How important is a diverse portfolio of ...

- 【Application】Highly adaptable 20MHz acti...

.9246509.png)

service@weylan-d.com

RM 705.7/F.FA YUEN COMM BLDGNO.75-77.FA YUEN STREET.MONGKOK.KLN.HONG KONG